Operating System – Direct Memory Access Long Questions Answers

Here in this section of Operating System Long Questions and Answers,We have listed out some of the important Long Questions with Answers on Direct Memory Access which will help students to answer it correctly in their University Written Exam.

Here in this section of Operating System Long Questions and Answers,We have listed out some of the important Long Questions with Answers on Direct Memory Access which will help students to answer it correctly in their University Written Exam.Lists of Long Descriptive type Questions that may be asked in Written Exams.

- (1) Explain the Direct Memory Access

Question-1 Explain the Direct Memory Access.

- CPU needs to address the device controllers to exchange data with them.

- CPU can request data from an I/O controller one byte at a time, which is wastage of time.

- So a different scheme called DMA (Direct Memory Access) is used. The operating system can only use DMA if the hardware has DMA controller.

- A DMA controller is available for regulating transfers to multiple devices.

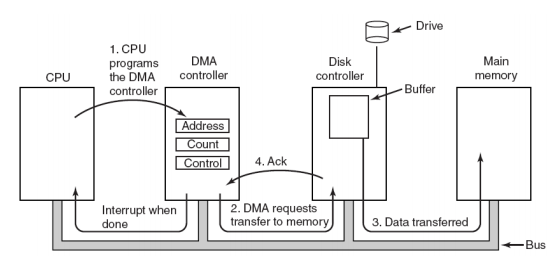

- The DMA controller has separate access to the system bus independent to CPU as shown in figure below. It contains several registers that can be written and read by CPU.

- These registers includes memory address register, a byte count register, one or more control registers.

Figure – Operation of a DMA transfer

Disk read-write without a DMA

- The disk controller reads the block from the drive serially, bit by bit, until the entire block is in the controller’s buffer.

- Next, it computes the checksum to verify that no read errors have occurred.

- Then the controller causes an interrupt, so that operating system can read the block from controller’s buffer (a byte or a word at a time) by executing a loop.

- After reading every single part of the block from controller device register, the operating system will store them into the main memory.

Disk read-write with DMA

- First the CPU programs the controller by setting its register so DMA knows what to transfer where.

- Simultaneously it issues a command to the disk controller telling it to read data from the disk into its internal buffer and perform the checksum.

- Data transfer is initiated by DMA through a read request from the bus to the disk controller. This read request looks like any other read request, and the disk controller does not know or care whether it came from the CPU or from a DMA controller.

- When writing is completed the disk controller will send an acknowledgement signal to DMA. DMA will then increment the memory address and decrement the byte count.

- Above process will be repeated until the byte count reaches to zero and after that DAM will interrupt the CPU to let it know that the transfer is now completed, so when the operating system starts up it does not have to wait for disk block as it is already there.

The buses can be operated in two modes:

- Word-at-a-time mode: Here the DMA requests for the transfer of one word and gets it. If CPU wants the bus at same time then it has to wait. This mechanism is known as Cycle Stealing as the device controller sneaks in and steals an occasional bus cycle from CPU, delaying it slightly.

- Block mod: Here the DMA controller tells the device to acquire the bus, issues a series of transfer and then releases the bus. This form of the operation is called Burst mode.It is more efficient then cycle stealing.

Disadvantages of DMA:

- Generally the CPU is much faster than the DMA controller and can do the job much faster so if there is no other work for it to do then CPU needs to wait for the slower DMA.